Рис. 3.37.Временная диаграмма записи в динамическое ОЗУ в режиме FPM

Еще одним способом увеличения быстродействия ОЗУ является применение микросхем EDO (Extended Data Out - ОЗУ с расширенным выходом данных). В EDO ОЗУ усилители-регенераторы не сбрасываются по окончанию строба CAS#, поэтому времени для считывания данных в таком режиме больше. Теперь для того чтобы сохранить время считывания на прежнем уровне, можно увеличить тактовую частоту системной шины и тем самым увеличить быстродействие компьютера. Для EDO ОЗУ цикл обращения к динамической памяти можно записать как 5-2-2-2.

Следующим шагом в развитии схем динамического ОЗУ было применение в составе ОЗУ счетчика столбцов. То есть при переходе адреса ячейки к следующему столбцу запоминающей матрицы адрес столбца инкрементируется (увеличивается) автоматически. Такое ОЗУ получило название BEDO (ОЗУ с пакетным доступом). В этом типе ОЗУ удалось достигнуть режима обращения к динамической памяти 5-1-1-1.

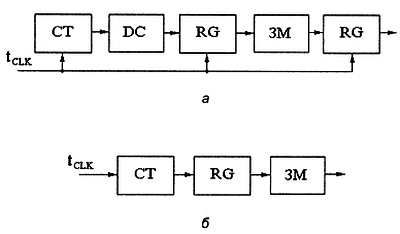

В синхронном динамическом ОЗУ (SDRAM) увеличение быстродействия получается за счет применения конвейерной обработки сигнала. Как известно, при использовании конвейера можно разделить операцию считывания или записи на отдельные подоперации, такие как выборка строк, выборка столбцов, считывание ячеек памяти, и производить эти операции одновременно. При этом пока на выход передается считанная ранее информация, производится дешифрация столбца для текущей ячейки памяти и производится дешифрация строки для следующей ячейки памяти. Этот процесс иллюстрируется рис. 3.38, а.

Из приведенного рисунка видно, что, несмотря на увеличение времени доступа к ОЗУ при считывании одной ячейки памяти, при считывании нескольких соседних ячеек памяти общее быстродействие микросхем синхронного динамического ОЗУ возрастает. Для сравнения на рис. 3.38, б приведена структурная схема обычного динамического ОЗУ.

Рис. 3.38.Структурная схема конвейерной обработки данных

Время задержки распространения сигнала tз в этой схеме равно периоду тактового сигнала в шине обращения к ОЗУ и определяется по формуле:

tз = tCT + tDC+ tЗМ,

где tCT - это время срабатывания счетчика адреса динамического ОЗУ; tDC - это время распространения сигнала дешифратора адреса; tЗМ - это время появления сигнала на выходе запоминающей матрицы.

Время задержки распространения сигнала в схеме синхронного динамического ОЗУ можно определить по формуле:

tз = tCT + tDC + tRG + tЗМ + tRG,

где tRG - это записи в параллельный регистр.

Таким образом, время доступа к синхронному динамическому ОЗУ больше, чем к обычному динамическому ОЗУ. Однако период тактового сигнала можно значительно уменьшить, т. к. он будет определяться максимальным из времен:

Поэтому, несмотря на то, что при обращении к одиночной ячейке памяти время доступа к SDRAM возрастает, при пакетном считывании последовательно расположенных байт общее время считывания оказывается значительно меньшим, т. к. все последующие данные на выходе ОЗУ будут появляться с периодом tобр. Выигрыш при пакетной работе SDRAM может быть достаточно большим, т. к. при обращении к этому типу памяти допустимо устанавливать размер пакета данных равным 256 слов.

На этом закончим рассмотрение различных видов памяти микропроцессорных устройств. Полученных знаний вполне достаточно для продолжения изложения материала. Если же кому-либо захочется более подробно ознакомиться с устройствами запоминания информации, можно обратиться к специализированной литературе [1, 3, 5–7].

Итак, подведем итоги

В данной главе были рассмотрены различные устройства хранения данных. Используя сумматоры, рассмотренные в предыдущей главе и запоминающие устройства, рассмотренные в этой главе, уже можно построить устройство обработки данных, входящее в состав любого микропроцессора.

А теперь научимся работать с двоичными числами: суммировать их, вычитать, работать со знаком и с дробными числами. Кроме того, пора бы научиться работать и с обычными текстами!

Глава 4

Принципы работы микропроцессора

Теперь рассмотрены принципы работы основных узлов микропроцессорной системы, и можно перейти к изучению операционного блока микропроцессора. Он предназначен для выполнения команд, т. е. реализует операции обработки данных. Однако прежде чем рассмотреть этот блок, давайте научимся представлять данные в двоичном виде и немного поучимся считать. Обратите внимание, что все примеры будут приведены в двоичном виде. Именно в такой форме выполняет обработку данных цифровая аппаратура. Здесь не будет использоваться шестнадцатеричная или восьмеричная форма записи двоичного кода. Эти формы записи двоичного числа удобны своею краткостью. Но для лучшего понимания принципов обработки данных удобней использовать двоичную запись.

Виды двоичных кодов

В микропроцессорах двоичные коды используются для представления любых обрабатываемых данных: чисел, текста, команд и т. д. При этом разрядность двоичных кодов может превышать разрядность внутренних регистров самого процессора и ячеек используемой памяти. В таком случае длинный код может занимать несколько ячеек памяти и обрабатываться несколькими командами процессора. Подчеркнем, что все ячейки памяти, выделенные под многобайтное число, рассматриваются как одно число.

Для представления числовых данных могут использоваться знаковые и беззнаковые коды. Для определенности примем разрядность процессора равной 8 битам, и в последующих примерах будем рассматривать именно такие числа.

Беззнаковые двоичные коды

Первый вид двоичных кодов, который мы рассмотрим, используется для представления целых беззнаковых чисел. В нем каждый двоичный разряд представляет собой степень цифры 2. Формат 8-разрядного беззнакового двоичного кода приведен на рис. 4.1.

Рис. 4.1. Формат 8-разрядного беззнакового двоичного кода

При этом минимально возможное число, которое можно записать таким двоичным кодом, равно 0. Максимально возможное число, которое можно представить этим кодом, можно определить как

М = 2 - 1

где n - разрядность двоичного числа. Разрядность числа обычно выбирают кратной разрядности микропроцессора.

Эти два числа полностью определяют диапазон значений чисел, которые можно представить двоичным кодом. В случае двоичного 8-разрядного беззнакового двоичного кода целые числа, которые можно записать с его помощью, находятся в диапазоне от 0 до 255. Восьмиразрядное двоичное число обычно называют байтом.

Для беззнакового двоичного 16-разрядного кода диапазон представляемых значений будет от 0 до 65535. В микропроцессорной системе, построенной на 8-разрядном процессоре, для хранения 16-разрядного числа используется две ячейки памяти, расположенные в соседних адресах. Для работы с числами, занимающими несколько ячеек памяти, используются специальные команды микропроцессора, позволяющие учитывать перенос между младшими и старшими байтами.

Прямые знаковые двоичные коды

Второй вид двоичных кодов, который мы рассмотрим, - это прямые целые знаковые коды. В этих кодах старший разряд в слове используется для представления знака числа. В прямом знаковом коде нулем обозначается знак "+", а единицей - знак "-". В результате введения знакового разряда диапазон чисел, представляемых двоичным кодом, смещается в сторону отрицательных чисел. Формат 8-разрядного прямого знакового двоичного кода приведен на рис. 4.2. На рисунке приведено шесть различных чисел, записанных в этом коде.