Рис. 2.4. Условное графическое обозначение цифрового элемента, выполняющего логическую функцию "И-НЕ"

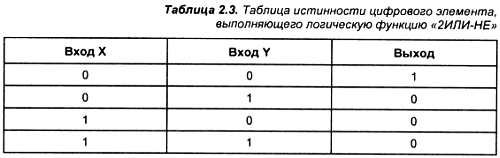

Точно так же, как редко можно встретить отдельный элемент логического "И", практически не производятся отдельные элементы логического "ИЛИ". Чаще встречаются элементы "2ИЛИ-НЕ", таблица истинности которых приведена в табл. 2.3.

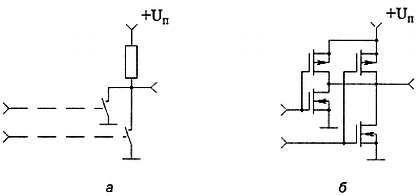

Как и в предыдущем случае, воспользуемся для реализации элемента "2ИЛИ-НЕ" ключами. На этот раз соединим ключи параллельно. Схема, реализующая таблицу истинности табл. 2.3, приведена на рис. 2.5, а. Схема логического элемента "2ИЛИ-НЕ", выполненного на КМОП-транзисторах, показана на рис. 2.5, б. Как видно из приведенных схем, уровень логического нуля появится на выходе любой из этих схем, как только любой из ключей будет замкнут, т. е. приведенные схемы реализуют таблицу истинности табл. 2.3.

Рис. 2.5.Принципиальные схемы элемента, реализующего логическую функцию "2ИЛИ-НЕ"

Так как один и тот же логический элемент может быть реализован различными способами, для его изображения на схемах используется специальное условное графическое обозначение, приведенное на рис. 2.6.

Рис. 2.6.Условное графическое обозначение элемента, выполняющего логическую функцию "2ИЛИ-НЕ"

Принципы реализации цифровых устройств по произвольной таблице истинности

Любое цифровое устройство полностью описывается таблицей истинности. При построении сложных устройств с произвольной таблицей истинности используется сочетание простейших элементов: "И" "ИЛИ" "НЕ". Если устройство имеет несколько выходов, то формирование сигнала для каждого из них анализируется отдельно и для каждого из них строится отдельная схема.

Для реализации устройства можно воспользоваться как элементами "И", так и элементами "ИЛИ". В настоящее время наиболее распространены микросхемы, совместимые с ТТЛ, а в ТТЛ проще всего получить элементы "И", выходы которых объединены по функции "ИЛИ", поэтому рассмотрим способ реализации произвольной таблицы истинности, основанный на комбинации логических элементов "И-ИЛИ".

Для реализации таблицы истинности при помощи логических элементов "И" достаточно рассмотреть только те ее строки, которые содержат логические единицы в выходном сигнале. Строки, содержащие в выходном сигнале логический ноль, в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую единицу, реализуется элементом логического "И" с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы, описанные в таблице истинности логической единицей, подаются на вход этого элемента непосредственно, а входные сигналы, описанные в таблице истинности логическим нулем, подаются на вход этого же элемента "И" через инверторы. Объединение сигналов с выходов элементов "И", реализующих отдельные строки таблицы истинности, производится при помощи элемента логического "ИЛИ".

Количество входов элемента "ИЛИ" определяется количеством строк таблицы истинности, в которых в выходном сигнале присутствует логическая единица.

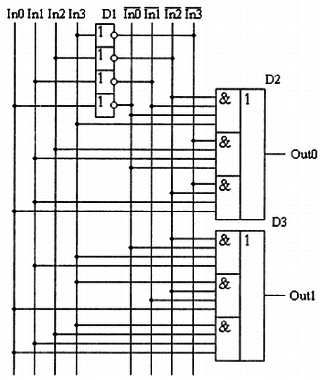

Для сокращения количества инверторов имеет смысл выделить их в отдельный блок, который сразу сформирует сигналы, инверсные по отношению к входным сигналам цифрового устройства. Теперь для реализации строки таблицы истинности достаточно соединить входы логического элемента "И" с соответствующими инвертированными и неинвертированными входными сигналами.

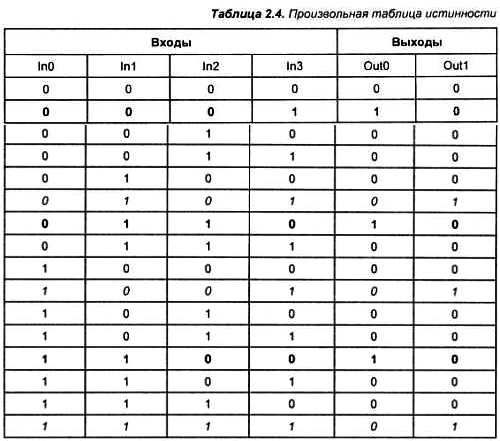

Рассмотрим конкретный пример. Пусть необходимо реализовать устройство с таблицей истинности, приведенной в табл. 2.4. Для построения схемы, реализующей сигнал Out1, достаточно рассмотреть строки, выделенные жирным шрифтом. Эти строки реализуются микросхемой D2 на рис. 2.7. Каждая строка реализуется своим многовходовым элементом "И", затем выходы этих элементов объединяются по "ИЛИ". Количество входов элемента "И" однозначно определяется числом входных сигналов в таблице истинности. Количество этих элементов, а значит и входов в логическом элементе "ИЛИ", определяется количеством строк с единичным сигналом на реализуемом выходе цифрового устройства.

Рис. 2.7. Принципиальная схема устройства, реализующего таблицу истинности, приведенную в табл. 2.4

Для построения схемы, реализующей сигнал Out2, достаточно рассмотреть строки, выделенные курсивом. Соответствующая логическая функция реализуется микросхемой D3. Принцип построения этой схемы такой же, как в примере, рассмотренном выше, и поэтому повторяться не будем.

Обычно при построении цифровых устройств после реализации таблицы истинности производится минимизация схемы, но для упрощения изложения материала в этой книге она выполняться не будет. Отказ от минимизации оправдан еще и тем, что неминимизированные схемы обычно обладают максимальным быстродействием.

Сумматоры

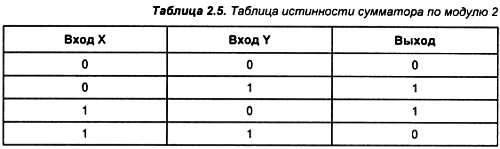

Важным элементом цифровых устройств, выполняющих арифметическую обработку цифровой информации, является сумматор. Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. В табл. 2.5 приведена таблица истинности этого сумматора. Ее можно получить, исходя из правил суммирования в двоичной арифметике. Предполагается, что читатель знаком с основами двоичной арифметики. Более подробно операции над двоичными числами будут рассмотрены позднее.

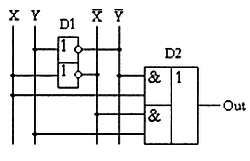

В соответствии с принципами построения произвольной таблицы истинности, рассмотренными в предыдущей главе, получим схему сумматора по модулю 2. Эта схема приведена на рис. 2.8.

Рис. 2.8.Принципиальная схема устройства, реализующего таблицу истинности сумматора по модулю 2

Сумматор по модулю 2 (для двоичной арифметики его функцию реализует элемент исключающего "ИЛИ") изображается на схемах с использованием условного графического обозначения, показанного на рис. 2.9.

Рис. 2.9.Условное графическое обозначение элемента, выполняющего логическую функцию исключающего "ИЛИ"

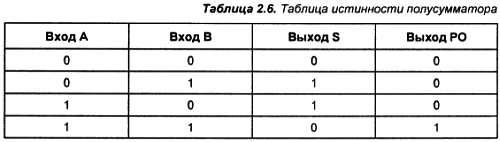

Сумматор по модулю 2 выполняет суммирование без учета переноса. В полном двоичном сумматоре его необходимо учитывать, поэтому требуются элементы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такого устройства, называемого полусумматором, приведена в табл. 2.6.

Обратите внимание, что сигналы в приведенной таблице истинности расположены в порядке, принятом для схем, т. е. в соответствии с тем, что сигнал распространяется слева направо. В результате перенос, который имеет двоичный вес, больший по сравнению с суммируемыми разрядами, записан правее. В математике принят другой порядок разрядов числа. Старший разряд на бумаге записывается самым левым, а младший разряд записывается самым правым. В результате может возникнуть путаница. Чтобы этого не произошло, приведу десятичный эквивалент каждой строки таблицы истинности полусумматора (табл. 2.6).

Первая строка получена из выражения 0 + 0 = 010 (002). Вторая строка получена из выражения 0 + 1 = 110 (012). Третья строка получена из выражения 1 + 0 = 110 (012). Четвертая строка получена из выражения 1 + 1 = 210(102).

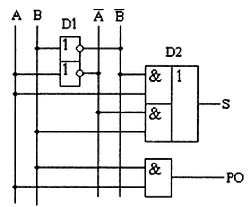

В соответствии с принципами построения произвольной таблицы истинности получим схему полусумматора. Она приведена на рис. 2.10. Условное графическое обозначение полусумматора показано на рис. 2.11.

Рис. 2.10.Принципиальная схема цифрового устройства, реализующего таблицу истинности полусумматора

Полусумматор формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому он и называется полусумматором.