Глава 3

Запоминающие устройства

В предыдущей главе были рассмотрены основные виды микросхем, используемых в цифровой технике. Однако мы собирались строить цифровые устройства на базе микропроцессорной техники. Пора обсудить, как устроены блоки, входящие в состав микропроцессоров.

Одной из важнейших задач при построении универсальных устройств обработки информации является запоминание различных видов данных. Для выполнения этой функции были разработаны несколько видов микросхем, отличающихся друг от друга. Отличие связано с требованиями, предъявляемыми к хранимым данным. Часть из них должна существовать длительное время, часто до тех пор, пока существует устройство.

Другая часть данных представляет интерес только в течение относительно короткого промежутка времени, в процессе работы устройства. В зависимости от этих требований различается и внутреннее устройство микросхем.

Достаточно часто при длительном хранении данных требуется только операция считывания. При этом их можно записать в процессе изготовления устройства. Поэтому такие микросхемы получили название постоянных запоминающих устройств. Так как в этих микросхемах производится только одна операция, то и внутреннее устройство у них проще. Именно по этой причине начнем изучение внутренней структуры запоминающих устройств с постоянных запоминающих устройств.

Постоянные запоминающие устройства

Очень часто в различных устройствах требуется хранение информации, которая не изменяется. Это программы в микроконтроллерах, начальные загрузчики и BIOS в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах. Практически всегда эта информация не требуется вся сразу, обычно требуется доступ к отдельным ее фрагментам.

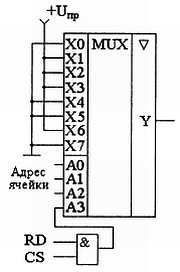

Простейшие устройства для запоминания постоянной информации можно построить на мультиплексорах. Схема такого постоянного запоминающего устройства приведена на рис. 3.1; это устройство содержит восемь одноразрядных ячеек памяти. Запоминание конкретного бита в одноразрядной ячейке производится присоединением соответствующего входа мультиплексора к источнику питания (высокий уровень - запись единицы) или к общему проводу (низкий уровень - запись нуля). Выбор конкретной ячейки памяти осуществляется при помощи адресных входов А0-А2. В приведенной на рис. 3.1 схеме - это входы управления мультиплексора.

Рис. 3.1.Схема постоянного запоминающего устройства, построенного на мультиплексоре

Обычно информация на выходе ПЗУ не требуется постоянно. Она должна быть предоставлена только по специальному запросу. Этот запрос формируется посредством сигнала чтения RD. Название этого сигнала расшифровывается как read (читать). Сигнал RD можно завести на внутренний дешифратор мультиплексора, как это показано на рис. 3.1. То есть содержимое ячейки памяти появится на выходе ПЗУ только при активном сигнале чтения RD. При всех других условиях выход микросхемы будет оставаться в высокоомном состоянии.

При построении устройств памяти обычно требуется иметь возможность расширения объема памяти. Это выполняется с помощью дополнительной микросхемы и дополнительной линии адресной шины. Кроме того, добавляется дешифратор адреса. Его нужно таким образом подключить к микросхемам памяти, чтобы он запрещал работу одной из микросхем памяти или разрешал работу другой в зависимости от адреса читаемой ячейки. Для подключения дополнительного дешифратора адреса служит еще один вход выбора кристалла CS (chip select - выбор кристалла). С точки зрения функционирования ПЗУ сигналы чтения RD и выбора кристалла CS не различаются, поэтому их можно объединить при помощи логического элемента "2И".

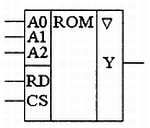

На схемах ПЗУ обозначается, как показано на рис. 3.2. На нем приведено условное графическое обозначение, соответствующее схеме рис. 3.1. Надпись "ROM" в среднем поле является сокращением от английских слов read-only memory (память, доступная только для чтения).

Рис. 3.2.Условное графическое обозначение постоянного запоминающего устройства

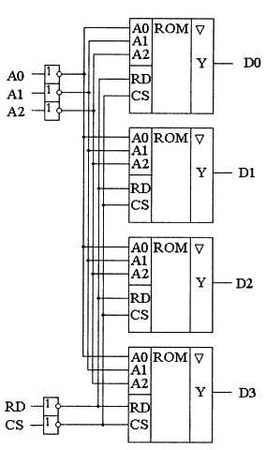

Для того чтобы увеличить разрядность ячейки памяти ПЗУ, одноразрядные микросхемы можно объединять. При этом параллельно соединяются одноименные адресные входы и входы сигналов управления RD и CS, a информационные выходы остаются независимыми. Схема объединения одноразрядных ПЗУ для реализации многоразрядного запоминающего устройства с восемью 4-разрядными ячейками приведена на рис. 3.3, а условное графическое обозначение 8-разрядного ПЗУ с 1024 ячейками памяти - на рис. 3.4.

Рис. 3.3.Схема многоразрядного ПЗУ

Как видно из приведенной схемы, адресные входы схемы объединяются параллельно. При этом возрастает общий входной ток микросхем памяти, протекающий по каждой линии адресной шины. Чтобы в результате не увеличивался входной ток запоминающего устройства, на адресных входах предусматривают усилители сигнала. В этом качестве можно использовать самые обыкновенные инверторы, как это показано на рис. 3.3. Точно с такой же целью поставлены инверторы и на управляющих входах чтения RD и выбора кристалла CS. При этом активными становятся низкие уровни этих сигналов.

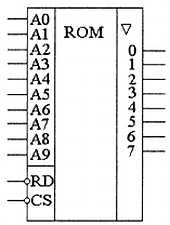

Масочные ПЗУ изображаются на схемах как показано на рис. 3.4. Активность низких уровней сигналов CS и RD обозначена кружками возле соответствующих управляющих входов.

Рис. 3.4.Условное графическое обозначение многоразрядного постоянного запоминающего устройства

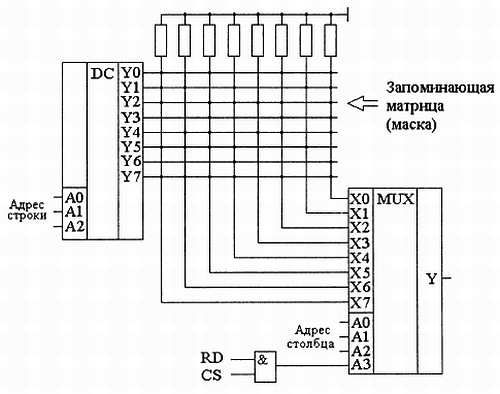

Запись информации в ПЗУ (микросхему, доступную только для чтения) производится при помощи последней операции изготовления микросхемы - металлизации. Она выполняется при помощи маски, поэтому такие микросхемы получили название масочных запоминающих устройств. Еще одно отличие реальных микросхем от упрощенной модели, приведенной выше, - это использование для дешифрации адреса кроме мультиплексора, еще и дешифратора. Такое решение позволяет превратить одномерную запоминающую структуру в двухмерную и тем самым существенно сократить объем схемы внутреннего дешифратора адреса. Реализация ПЗУ с двухмерной структурой запоминающих элементов показана на рис. 3.5.

Рис. 3.5.Схема масочного постоянного запоминающего устройства с двухмерной матрицей запоминающих элементов

Рассмотрим подробнее работу этого ПЗУ. В отличие от схемы, приведенной на рис. 3.1, в данном случае не используется непосредственное соединение входов мультиплексора с общим проводом. Вместо этого подключение производится через резистор. В результате, если с выхода дешифратора не будет подан единичный уровень, то на входе мультиплексора будет присутствовать уровень логического нуля. Запись логической единицы в ячейку ПЗУ производится соединением линий выхода дешифратора и входа мультиплексора в точке их пересечения. Если же в ячейку необходимо записать логический ноль, то соединение цепей не производится. Именно такая запоминающая структура получила название "матрица".

Приведенная на рис. 3.5 схема реализует одноразрядное ПЗУ с 64 одноразрядными ячейками памяти. Рассмотрим, какая информация хранится в этом ПЗУ. При выборе нулевой ячейки памяти на адресные входы дешифратора будут поданы три младших разряда адреса, т. е. код 000. В результате единичный уровень появится на выходе Y0. На адресные входы мультиплексора будут поданы старшие три разряда адреса. В нашем примере они тоже равны нулю. В результате мультиплексор передаст на выход сигнал со своего входа Х0. Так как на схеме эти цепи соединены между собой, то на выходе ПЗУ появится логическая единица.

Теперь рассмотрим считывание восьмой ячейки памяти. Здесь, как и в предыдущем случае, младшие три разряда адреса равны 0. Поэтому дешифратор выдаст единицу на линию Y0. Мультиплексор же получит код 001, поэтому на выход будет подключен вход XI. Эти цепи между собой не соединены, поэтому на выход будет выдан уровень логического нуля.

Для реализации многоразрядного ПЗУ необходимо использование нескольких матриц, подобных приведенной на рис. 3.5. Объединение матриц производится согласно схеме рис. 3.3.