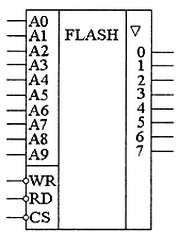

Рис. 3.10. Условное графическое обозначение FLASH-памяти

Использование блочного стирания позволяет уменьшить сложность внутреннего устройства управления микросхем, поэтому FLASH-ПЗУ предоставляют максимальный объем матрицы запоминающих элементов. Кроме того, эти микросхемы обладают значительно меньшей стоимостью по сравнению с электрически стираемыми ПЗУ. В настоящее время FLASH-ПЗУ постепенно вытесняют все остальные виды постоянных запоминающих устройств за исключением электрически стираемых ПЗУ.

Рассмотренные виды памяти позволяют хранить информацию практически неограниченно долго. Тем не менее, они не обладают максимальным быстродействием, поэтому, кроме постоянных запоминающих устройств, используются более быстродействующие микросхемы, теряющие свое содержимое при выключении питания. Эти микросхемы обладают большим быстродействием по сравнению с ПЗУ и в них записывают результаты предварительных вычислений или информацию, нужную только в определенный момент времени. Например, набранный номер вызываемого абонента в сотовом аппарате или выбранный номер телевизионной программы в телевизоре.

Для хранения информации можно воспользоваться элементами, которые сохраняют напряжение на своем выходе до тех пор, пока подается питание. Элементы, которые могут запоминать двоичные логические уровни, получили название "триггеры". Рассмотрим подробнее, как устроены подобные устройства.

Триггеры

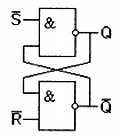

Простейшая схема, позволяющая запоминать двоичную информацию, строится на основе простейших логических элементов "ИЛИ" или "И", описанных в главе 1. Такая схема, построенная на элементах "И", приведена на рис. 3.11. Выход триггера Q можно установить в единичное состояние при подаче на его вход S (Set) логического нуля. Сбросить выход триггера Q в нулевое состояние можно, подав на его вход R (Reset) логический ноль. Это состояние сохраняется до подачи очередного сигнала R или S либо до выключения напряжения питания схемы.

Так как описанный триггер можно только устанавливать в единичное значение или сбрасывать в нулевое значение, он получил название RS-триггер.

Рис. 3.11.Схема простейшего триггера на элементах "И"

Входы R и S инверсные (активный уровень '0')

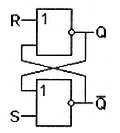

Такой триггер можно построить и на логических элементах "ИЛИ". Такая схема приведена на рис. 3.12. Единственное отличие от схемы рис. 3.11 будет заключаться в том, что сброс и установка триггера осуществляются единичными логическими уровнями.

Рис. 3.12.Схема простейшего триггера на элементах "ИЛИ"

Входы R и S прямые (активный уровень '1')

Так как триггер при построении его на различных логических элементах работает одинаково, то его изображают на схемах тоже одинаково.

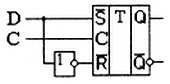

Условное графическое обозначение RS-триггера приведено на рис. 3.13.

Рис. 3.13.Условное графическое обозначение простейшего триггера

Триггер позволяет запоминать логический сигнал, но при изменении сигнала на входе устройства может возникать переходный процесс (в цифровых схемах это явление называют гонками или состязаниями), в ходе которого сигнал на входе триггера может принимать случайные значения. Это может привести к ошибкам, для предотвращения которых запоминание входного сигнала должно происходить после окончания всех переходных процессов. То есть цифровые схемы требуют синхронизации. Все переходные процессы в цифровой схеме должны закончиться до поступления синхросигнала, иначе цифровое устройство будет работать с ошибками.

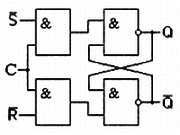

В синхронных цифровых схемах используются синхронные триггеры. Для построения такого триггера можно воспользоваться логическим элементом "И", ведь он может работать как электронный ключ (см. построение мультиплексора на рис. 2.18). Схема синхронного RS-триггера приведена на рис. 3.14, а его условное графическое обозначение - на рис. 3.15.

Рис. 3.14.Схема синхронного триггера на схемах "И"

Рис. 3.15.Условное графическое обозначение синхронного триггера

В дальнейшем именно это обозначение и будет использоваться на схемах более сложных запоминающих устройств.

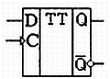

В приведенных схемах триггеров для записи логического нуля и логической единицы требуется подавать сигналы на разные входы, что не всегда удобно, поэтому для запоминания дискретной информации применяются D-триггеры, имеющие один информационный вход. В D-триггере достаточно подать на вход D сигнал, который необходимо запомнить, и синхроимпульс - на вход синхронизации С. Схема такого триггера приведена на рис. 3.16, а условное графическое обозначение - на рис. 3.17.

Рис. 3.16.Схема D-триггера со статическим управлением (защелки)

Рис. 3.17. Условное графическое обозначение D-триггера со статическим управлением (защелки)

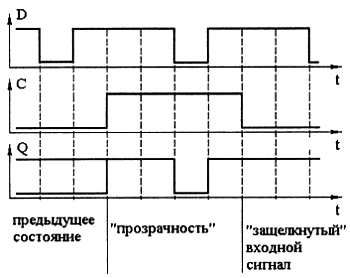

Во всех приведенных схемах триггеров запоминание сигнала происходит по уровню синхросигнала, поэтому они называются D-триггерами со статическим управлением, или триггерами-защелками. Легче всего объяснить появление этого названия по временным диаграммам, приведенным на рис. 3.18.

Рис. 3.18.Временные диаграммы D-триггера со статическим управлением (защелки)

Как видно из рисунка, триггер-защелка хранит данные только при нулевом уровне на входе синхронизации С. Если же на этот вход подать активный высокий уровень, то напряжение на выходе триггера будет повторять входной сигнал. Входное напряжение запоминается только в момент изменения уровня сигнала синхронизации С с высокого на низкий. Входные данные как бы "защелкиваются" в этот момент, отсюда и название - триггер-защелка.

В этой схеме переходный процесс входного информационного сигнала (D) может беспрепятственно проходить на выход триггера. Поэтому там, где важно избежать этого, необходимо сокращать длительность импульса синхронизации до минимума. Только в этом случае переходный процесс практически не сможет появиться на выходе триггера.

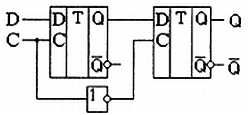

Чтобы преодолеть такое ограничение на длительность синхронизирующего импульса, были разработаны триггеры, работающие по фронту синхросигнала. Схема такого триггера приведена на рис. 3.19, а его условное графическое обозначение - на рис. 3.20.

Рис. 3.19.Схема D-триггера с управлением по фронту

Рис. 3.20. Условное графическое обозначение D-триггера с управлением по фронту

Как видно из схемы D-триггера с управлением по фронту, приведенной на рис. 3.19, на ее выходе не могут появиться переходные процессы, т. к. если их пропускает первый триггер, то не пропустит второй, который в это время находится в режиме хранения. И наоборот, если второй триггер пропускает сигнал со своего входа на выход, то первый триггер находится в режиме хранения и, значит, сигнал на входе второго триггера не может измениться.

Из рис. 3.19 видно, что схема триггера с управлением по фронту сложнее, чем у триггера-защелки, а это означает, что D-триггер с управлением по фронту будет дороже, а его быстродействие - ниже, чем у триггера-защелки.