Регистры

Триггеры позволяют запоминать одноразрядное двоичное слово. Однако в ряде случаев требуется запоминать двоичные слова большей разрядности. Это позволяют сделать регистры.

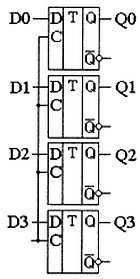

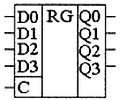

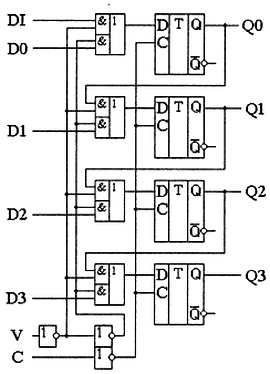

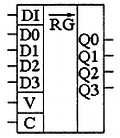

Регистром называется последовательное или параллельное соединение любых устройств, будь то клавиши музыкального инструмента, набор букв печатающей машинки или триггеры в цифровой технике. Регистры обычно строятся на основе D-триггеров. При этом для построения регистров могут использоваться как D-триггеры с управлением по фронту, так и триггеры-защелки. При использовании для этого защелок регистр называется регистром-защелкой. Параллельный регистр служит для запоминания многоразрядного двоичного слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырехразрядного параллельного регистра, построенного на D-триггерах, приведена на рис. 3.21, а его условное графическое обозначение - на рис. 3.22.

Рис. 3.21.Схема 4-разрядного параллельного регистра

Рис. 3.22.Условное графическое обозначение 4-разрядного параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) записываются одновременно, поэтому входы синхронизации всех триггеров можно соединить параллельно.

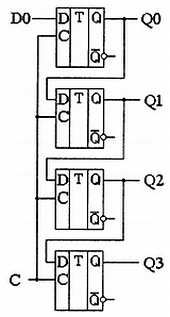

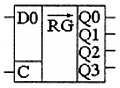

Кроме параллельных, в цифровой технике используются последовательные регистры. Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Схема регистра, осуществляющего преобразование последовательного кода в параллельный, приведена на рис. 3.23, а его условное графическое обозначение - на рис. 3.24.

Рис. 3.23.Схема последовательного регистра

Рис. 3.24.Условное графическое обозначение последовательного регистра

В схеме, приведенной на рис. 3.23, информация, поступившая на вход первого триггера сдвигового регистра D0, будет переписываться в следующий триггер при поступлении очередного синхронизирующего импульса. Таким образом, после четырех тактовых импульсов на выходах сдвигового регистра окажется записанной информация, присутствовавшая на входе регистра в моменты поступления этих тактовых импульсов.

Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы, что позволяет преобразовывать двоичный код из параллельной формы в последовательную. Это свойство универсального последовательно-параллельного регистра используется, например, для реализации последовательного порта в микропроцессорной системе. Схема универсального последовательно-параллельного регистра приведена на рис. 3.25, а его условное графическое обозначение - на рис. 3.26.

Рис. 3.25.Схема универсального последовательно-параллельного регистра

Рис. 3.26.Условное графическое обозначение универсального последовательно-параллельного регистра

Переключение регистра из параллельного режима в последовательный и наоборот осуществляется при помощи мультиплексора, построенного на элементах 2И-2ИЛИ (рис. 3.25). В зависимости от управляющего сигнала V он подключает к входу каждого D-триггера либо выход предыдущего триггера, либо параллельный вход универсального регистра. При подаче на вход управления V логической единицы регистр будет работать как параллельный, а при подаче логического нуля - как последовательный.

Если читателю покажется непонятной работа коммутатора, собранного на элементах 2И-2ИЛИ, то имеет смысл заново перечитать описание работы мультиплексора в главе 2.

Статические оперативные запоминающие устройства (ОЗУ)

В радиоаппаратуре часто требуется хранение временной информации, значение которой не важно при включении устройства. Такую память можно было бы построить на микросхемах EEPROM- или FLASH-памяти, но, к сожалению, эти микросхемы дороги, характеризуются сравнительно малым количеством циклов перезаписи, а также чрезвычайно низким быстродействием при считывании и особенно при записи информации. Для хранения временной информации можно воспользоваться параллельными регистрами.

Устройства памяти, в которых в качестве запоминающих ячеек используются параллельные регистры, называются статическими ОЗУ, т. к. информация в них сохраняется все время, пока к микросхеме подключено питание. Кроме микросхем статических ОЗУ, существуют микросхемы динамических ОЗУ, где в качестве запоминающих ячеек используются конденсаторы. В отличие от микросхем статического ОЗУ, в микросхемах динамического ОЗУ постоянно требуется регенерировать их содержимое, иначе из-за разряда конденсаторов информация будет испорчена. Эти микросхемы будут рассмотрены позднее.

Так как запоминаемые слова не нужны одновременно, то в ОЗУ можно воспользоваться механизмом адресации, который уже рассматривался ранее при объяснении принципов работы ПЗУ.

В микросхемах статических ОЗУ присутствуют две операции: запись и чтение. Для их выполнения можно использовать различные шины данных (как это делается в сигнальных процессорах), но чаще используется одна и та же шина. Это позволяет экономить выводы микросхем, подключаемых к этой шине, и легко осуществлять коммутацию сигналов между различными устройствами.

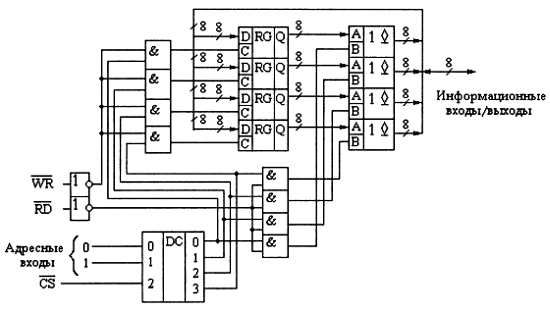

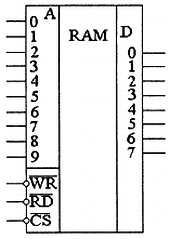

Схема статического ОЗУ приведена на рис. 3.27. Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя. Естественно, что схемы реальных ОЗУ будут иными, чем приведенная на этом рисунке. Тем не менее, она позволяет понять, как работает реальное ОЗУ статического типа. Условное графическое обозначение ОЗУ на схемах приведено на рис. 3.28.

Рис. 3.27.Структурная схема ОЗУ

Рис. 3.28.Условное графическое обозначение ОЗУ

На схеме рис. 3.27 для обозначения того, что используется инвертированный сигнал или сигнал с активным низким уровнем, над именем цепи проставляется черта. К сожалению, в обычном тексте затруднительно использовать такую же черту. Поэтому для обозначения таких сигналов в книге используется два способа: символ подчеркивания перед именем цепи (_WR) или символ # после имени (WR#).

Сигнал записи WR# позволяет записать логические уровни, присутствующие на информационных входах, во внутреннюю ячейку ОЗУ. Сигнал чтения RD# позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. В приведенной на рис. 3.27 схеме невозможно одновременно производить операцию записи и чтения, но это в большинстве случаев и не нужно. Схема на рис. 3.27 ориентирована на применение микропроцессорной системы с одной шиной, по которой в разные моменты времени будет осуществляться или запись, или чтение информации.

Конкретная ячейка микросхемы, в которую будет записываться информация, выбирается при помощи двоичного кода - адреса ячейки. Объем памяти микросхемы зависит от количества ячеек, содержащихся в ней.

Количество адресных выводов микросхемы ОЗУ однозначно определяется количеством находящихся в ней ячеек памяти. Исходя из этого, количество ячеек памяти М в микросхеме можно определить по количеству адресных выводов N. Для этого необходимо возвести число 2 в степень, равную количеству адресных выводов микросхемы:

М = 2

Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ. Пример объединения четырех микросхем ОЗУ с помощью дешифратора приведен на рис. 3.29. При этом общий объем памяти увеличивается в четыре раза.